Output Triggering Technology

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

| | | | |

||||||||||||||||||

One-Shot Triggering with Channel-List-Clocking Updates

This configuration can update all analog output channels in rapid sequence based on the internal clock. This pattern of updates is repeated each time the external clock goes active, and the entire process can be initiated by triggering.

Related |

|---|

|

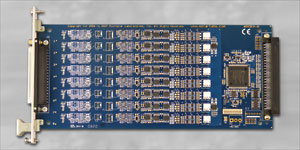

Don't let industrial strength interference use ground connections to corrupt both your output and input signal quality. The MSXB076 board, with fully isolated outputs, offers a solution. |

Notes:

- Clocking can start when trigger is held active high at least

tTrigMin - External clock cycle must be at least

tSynch + Nchannels x TIME specification - All clock levels must be held for at least

tExtClkPW - Clocking activity begins

tTCsetupafter triggering goes active - Data from buffer must be fetched and stable at converter before clocking

- The first update is latched at the external clock edge

- Next sample after interval

TIMEplus synchronizing delay up totSynch - Subsequent update values latched for conversion at internal clock edges

- Analog output values stabilize after settling transient

- Software control suspends internal clocking at end of channel list

- Updating for the next channel list cycle resumes on the next external clock edge.